# XN-1SSI Technology Module

# Imprint

## Manufacturer

Eaton Automation AG Spinnereistrasse 8-14 CH-9008 St. Gallen Switzerland www.eaton-automation.com www.eaton.com

#### Support Region North America

Eaton Corporation Electrical Sector 1111 Superior Ave. Cleveland, OH 44114 United States 877-ETN-CARE (877-386-2273) www.eaton.com

#### **Other regions**

Please contact your supplier or send an E-Mail to: <u>automation@eaton.com</u>

## **Original manual**

The German version of this document is the original manual.

## Translations of the original manual

All non-German editions of this document are translations of the original manual.

## **Editorial department**

Monika Jahn

## Brand and product names

All brand and product names are trademarks or registered trademarks of the owner concerned.

## Copyright

© Eaton Automation AG, CH-9008 St. Gallen

All rights reserved, also for the translation.

None of this document may be reproduced or processed, duplicated or distributed by electronic systems in any form (print, photocopy, microfilm or any other process) without the written permission of Eaton Automation AG, St. Gallen.

Subject to modifications.

# Warning!

Dangerous electrical voltage!

#### Before commencing the installation

- Disconnect the power supply of the device.

- Ensure that the device cannot be accidentally restarted.

- Verify isolation from the supply.

- Earth and short circuit.

- Cover or enclose neighbouring units that are live.

- Follow the engineering instructions of the device concerned.

- Only suitably qualified personnel in accordance with EN 50110-1/-2 (DIN VDE 0105 Part 100) may work on this device.

- Before installation and before touching the device ensure that you are free of electrostatic charge.

- The functional earth (FE) must be connected to the protective earth (PE) or tothe potential equalisation. The system installer is responsible for implementing this connection.

- Connecting cables and signal lines should be installed so that inductive or capacitive interference do not impair the automation functions.

- Install automation devices and related operating elements in such a way that they are well protected against unintentional operation.

- Suitable safety hardware and software measures should be implemented for the I/O interface so that a line or wire breakage on the signal side does not

result in undefined states in the automation devices.

- Ensure a reliable electrical isolation of the low voltage for the 24 volt supply. Only use power supply units complying with IEC/HD 60364-4-41 (DIN VDE 0100 Part 410).

- Deviations of the mains voltage from the rated value must not exceed the tolerance limits given in the specifications, otherwise this may cause malfunction and dangerous operation.

- Emergency stop devices complying with IEC/EN 60204-1 must be effective in all operating modes of the automation devices. Unlatching the emergency-stop devices must not cause uncontrolled operation or restart.

- Measures should be taken to ensure the proper restart of programs interrupted after a voltage dip or failure. This should not cause dangerous operating states even for a short time. If necessary, emergency-stop devices should be implemented.

- Wherever faults in the automation system may cause damage to persons or property, external measures must be implemented to ensure a safe operating state in the event of a fault or malfunction (for example, by means of separate limit switches, mechanical interlocks etc.).

# Safety regulations

- The electrical installation must be carried out in accordance with the relevant regulations (e.g. with regard to cable cross sections, fuses, PE).

- All work relating to transport, installation, commissioning and maintenance must only be carried out by qualified personnel. (IEC/HD 60364 (DIN VDE 0100) and national work safety regulations).

# **Table of contents**

|   | Table of contents                                                              | 5  |

|---|--------------------------------------------------------------------------------|----|

|   | About This Manual                                                              |    |

|   | Writing conventions                                                            | 9  |

| 1 | Product Description                                                            |    |

|   | General product description                                                    |    |

|   | - Power supply                                                                 |    |

|   | - Transmission procedure                                                       |    |

|   | – Data exchange                                                                |    |

|   | - Internal registers - read and write operations                               |    |

|   | <ul> <li>Register access and meaning</li> </ul>                                |    |

|   | - Comparison value 1, Comparison value 2                                       |    |

|   | – Lower limit, upper limit                                                     |    |

|   | - Offset function / load value                                                 |    |

|   | - Status messages of the SSI encoder                                           |    |

|   | Resetting the register bank                                                    |    |

|   | Technical features                                                             |    |

|   | Block diagram of the XN-1SSI     Tophnical data of the XN 1SSI                 |    |

|   | <ul> <li>Technical data of the XN-1SSI</li> <li>Indication elements</li> </ul> |    |

|   | Base modules.                                                                  |    |

|   | - Technical data of the base modules                                           |    |

|   | <ul> <li>Connection diagram for the SSI encoder</li> </ul>                     |    |

|   |                                                                                | 52 |

| 2 | Integrating the Module in PROFIBUS-DP                                          | 33 |

|   | PROFIBUS-DP data image                                                         |    |

|   | - Process input                                                                |    |

|   | - Process output                                                               |    |

|   | - Diagnostics                                                                  |    |

|   | – Parameters                                                                   |    |

|   | <ul> <li>Error detection / messages</li></ul>                                  |    |

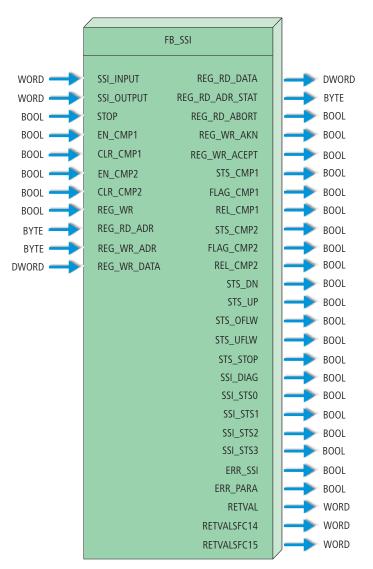

|   | Function block for SIMATIC S7                                                  | 49 |

|   |                                                                                |    |

3

4

| Integrating the Module in DeviceNet                                                                                                                                                            |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Process image                                                                                                                                                                                  |      |

| SSI Module Class (VSC116)                                                                                                                                                                      | . 59 |

| Integrating the Module in CANopen                                                                                                                                                              | . 77 |

| Introduction                                                                                                                                                                                   | . 77 |

| - General                                                                                                                                                                                      | . 77 |

| - Encoder-specific default PDOs                                                                                                                                                                | . 78 |

| Encoders Device Profile Implementation                                                                                                                                                         |      |

| - Overview of Encoders Device Profile Range                                                                                                                                                    | . 79 |

| - Object 5800hex - Encoder Basic Mode                                                                                                                                                          | . 81 |

| - Object 5801hex - Encoder Config                                                                                                                                                              | . 81 |

| <ul> <li>Object 5800hex – Encoder Basic Mode.</li> <li>Object 5801hex – Encoder Config</li> <li>Object 5802hex – Encoder Status</li> </ul>                                                     | . 84 |

| <ul> <li>Object 5803hex – Encoder Flags</li></ul>                                                                                                                                              | . 85 |

| – Object 5804hex – Encoder Diag                                                                                                                                                                | . 87 |

| - Object 5805hex - SSI Native Status                                                                                                                                                           |      |

| - Object 5806hex - SSI Optional Encoder Status                                                                                                                                                 |      |

| - Object 5808hex - Encoder Control                                                                                                                                                             |      |

| - Object 5810hex - Counter Load Prepare Value                                                                                                                                                  |      |

| - Object 5811hex - Counter Pulse Width                                                                                                                                                         |      |

| - Object 5820hex - Measuring Integration Time                                                                                                                                                  |      |

| - Object 5821hex - Measuring Low Limit                                                                                                                                                         |      |

| - Object 5822hex - Measuring High Limit                                                                                                                                                        |      |

| - Object 5823hex - Measuring Units per Revolution                                                                                                                                              |      |

| - Object 5840hex - SSI Diag Mapping                                                                                                                                                            |      |

| - Object 6800hex - Operating Parameters                                                                                                                                                        | . 9/ |

| - Object 6810hex - Preset Values                                                                                                                                                               | 07   |

| for Multi-Sensor Devices                                                                                                                                                                       | . 9/ |

| <ul> <li>Object 6820hex – Position Value</li> <li>Object 6800hex – CAM State Register</li> <li>Object 6801hex – CAM Enable Register</li> <li>Object 6802hex – CAM Polarity Register</li> </ul> | . 98 |

| - UDJect obuunex - CANI State Register                                                                                                                                                         | . 99 |

| - UDJect ODUTITEX - CAM Enable Register                                                                                                                                                        | 100  |

| <ul> <li>Object object object and rolarity negister</li> <li>Object 6B10hex – CAM1 Low Limit</li> </ul>                                                                                        | 101  |

| <ul> <li>Object OBTONEX – CAMT Low Limit</li> <li>Object 6B20hex – CAM1 High Limit</li> </ul>                                                                                                  | 101  |

| <ul> <li>Object 0B20hex - CANT High Limit</li> <li>Object 6B30hex - CAM1 Hysteresis</li> </ul>                                                                                                 |      |

| <ul> <li>Object 0D30hex - CANT Hysteresis</li> <li>Object 6D00hex - Operating Status</li> </ul>                                                                                                |      |

| <ul> <li>Object 0D00hex - Operating Status</li></ul>                                                                                                                                           | 100  |

| Measuring Step (linear)                                                                                                                                                                        | 103  |

|                                                                                                                                                                                                | 100  |

| <ul> <li>Additional emergencies</li></ul>                                     |  |

|-------------------------------------------------------------------------------|--|

| <ul> <li>Object 6D02hex - Number of<br/>distinguishable revolutions</li></ul> |  |

Table of contents

# **About This Manual**

#### Writing conventions

Symbols used in this manual have the following meanings:

## Note!

Warns of a hazardous situation that could result in slight damage to the product or components.

# Caution!

Warns of the possibility of a hazardous situation that could result in major damage and minor injury.

# Warning!

Warns of the possibility of a hazardous situation that could result in major damage and serious or fatal injury or even death.

Indicates interesting tips and additional information. About This Manual Writing conventions

# General product description

The XN-1SSI technology module is an addition to the XI/ON range of components in slice design. It is used for connecting SSI encoders with a maximum word length of 32 bits and a maximum bit transmission rate of 1Mbit/s. The module provides a 24 V DC (500 mA) power supply. In order to read SSI encoder data, the XN-1SSI module outputs a clock signal with which the encoder value can be read via the signal input. The clock signal and the signal input are based on the RS422 protocol.

The module can be fitted or removed during operation without damaging the module electronics. Once the module is removed or fitted, this is detected with the next telegram, the module list is updated and communication with all modules of the station is restored. Communication is maintained for as long as no more than two adjacent modules have been removed. Removing the electronics module will cause the power supply of the SSI encoder to be disconnected from the field voltage.

#### **Power supply**

The connected SSI encoder is fed with power via the output terminals of the SSI module. The power supplied to the XN-PF-24VDC-D power feeding module and XN-BR-24VDC-D bus refreshing module is distributed via the bus system and connected directly to the output terminals. The module bus electronics unit is fed by the module bus.

# 1 Product Description General product description

#### **Transmission procedure**

The XN-1SSI module enables the SSI data to be transferred according to the requirements of the application. The parameters of the XN-1SSI module can be configured by the user to set up a functional transmission procedure as required.

Gray code or binary code data transmission is possible.

Bit transmission rates from 62.5 Kbit/s to 1 Mbit/s are possible.

The SSI encoder value can be represented in a data frame with between 1 to 32 bits. Bits can be deactivated at both the LSB and MSB side of the frame. At the MSB side this is done by a masking operation, which causes invalid bits to be set to 0. At the LSB side, the invalid bits are removed by shifting the entire data frame to the right. The missing bits on the MSB side are filled with zeros.

#### Data exchange

The process output data is transmitted from the PLC to the XN-1SSI module, whilst the process input data is transferred from the XN-1SSI module to the PLC.

The process output data is used for writing the registers and requesting data from them. It is possible to stop the communication with the SSI encoder and activate or deactivate comparison operations.

The process input data is used for reading the contents of the registers inside the modules. In this case, the SSI encoder value is part of the register. The writing of these registers can be controlled. The results of different comparison operations can be supplied, and the communication status with the SSI encoder can also be

displayed. Status messages that were generated by the connected SSI encoder can be passed to the PLC as process input data.

The diagnostics messages are also embedded in the process input data.

The parameter and diagnostics interface allows acyclic data to be transferred in addition to this cyclic data. The parameters for the data transmission on the SSI module, such as bit transmission rate, telegram length etc. are set via the parameter interface. The diagnostics interface supplies the higher-level system with error messages, such as parameter errors.

#### Internal registers - read and write operations

The SSI module is provided with a universal register interface that enables access to up to 64 registers. These are accessed via the process data.

For write access, it must be ensured beforehand that the register write interface is in the default status and that a write access operation is therefore not currently active. This is ensured if REG\_WR = 0 in the process output data, and is confirmed in the process input data with REG\_WR\_AKN = 0. Write access is then possible. The following values must be transferred with the process output data for this:

REG\_WR\_ADR = Register address, REG\_WR\_DATA = Value to be written (32 bit) REG\_WR = 1 (write command)

The SSI module acknowledges the processing of the write command via the process input data by signalling  $REG_WR_AKN = 1$ .

REG\_WR\_ACEPT = 1 in the process input data confirms whether the write operation to the

# 1 Product Description General product description

register was successfully completed. If the register could not be written (no access authorisation, out of value range, ...), this is indicated by REG\_WR\_ACEPT = 0. The write operation must then be terminated by REG\_WR = 0 in order to resume the default state.

The address specified at REG\_RD\_ADR of the process output data is used for read access. The read register content is entered in REG\_RD\_DATA (bytes 4-7) if the address at REG\_RD\_ADR was accepted in the process input data and if REG\_RD\_ABORT = 0 confirms that the register was read error-free. REG\_RD\_ABORT = 1 indicates that the register could not be read. REG\_RD\_ADR in the process input data then contains the address that could not be accessed successfully. The user data is then set to ZERO.

# 1 Product Description General product description

# **Register access and meaning**

| Designation   |    | Description                           | Default (HEX)   |

|---------------|----|---------------------------------------|-----------------|

| REG_SSI_POS   | 0  | Actual binary SSI encoder value       |                 |

| REG_MAGIC_NO  | 1  | Magic number (0xaa55cc33)             |                 |

| REG_HW_VER    | 2  | Hardware version                      |                 |

| REG_SW_VER    | 3  | Software version                      |                 |

| REG_SF        | 4  | Special Function register             |                 |

| REG           | 5  | Reserve                               |                 |

|               |    |                                       |                 |

| REG           | 13 | Reserve                               |                 |

| REG_WR_ADR    | 14 | Pointer register OUT                  |                 |

| REG_RD_ADR    | 15 | Pointer register IN                   |                 |

| REG_DIAG1     | 16 | Diagnostics data                      |                 |

| REG           | 17 | Reserve                               |                 |

|               | ·  |                                       |                 |

| REG           | 19 | Reserve                               |                 |

| REG_PARA1     | 20 | Parameter data                        | 0 x19 01 00 00  |

| REG           | 21 | Reserve                               |                 |

|               |    |                                       |                 |

| REG           | 31 | Reserve                               |                 |

| REG_GRAY_POS  | 32 | Actual Gray-coded SSI encoder value.  |                 |

| REG_SSI_FRAME | 33 | Complete frame read from SSI encoder. |                 |

| REG_CMP1      | 34 | Comparison value 1                    | 0 × 00 00 00 00 |

| REG_CMP2      | 35 | Comparison value 2                    | 0 × 00 00 00 00 |

| REG           | 36 | Reserve                               |                 |

|               |    |                                       |                 |

| REG           | 47 | Reserve                               |                 |

General product description

| Designation            |       |                            |     | Description                                   |                               |                          |     | Default (HEX)                 |  |  |

|------------------------|-------|----------------------------|-----|-----------------------------------------------|-------------------------------|--------------------------|-----|-------------------------------|--|--|

| REG_LOWER_LIMI 48<br>T |       |                            | Lov | Lower limit                                   |                               |                          |     | 0 × 00 00 00 00               |  |  |

| REG_UPPER_             | LIMIT | 49                         | Up  | per limit                                     |                               |                          | 0 x | FF FF FF FF                   |  |  |

| REG_OFFSET             |       | 50                         | Off | set value                                     |                               |                          | 0 x | 00 00 00 00                   |  |  |

| REG_SSI_MA             | SK    | 51                         | nos | ection of the<br>stics transfer<br>interfaces | 0 x                           | 00 00 00 00              |     |                               |  |  |

| REG                    |       | 52                         | Res | serve                                         |                               |                          |     |                               |  |  |

|                        |       |                            |     |                                               |                               |                          |     |                               |  |  |

| REG                    |       | 63                         | Res | serve                                         |                               |                          |     |                               |  |  |

| Designation            |       | Proces<br>outpu<br>interfa | t   | Storage<br>in<br>module                       | Process<br>input<br>interface | Param<br>eter<br>interfa |     | Diagnos-<br>tics<br>interface |  |  |

| REG_SSI_<br>POS        | 0     |                            |     |                                               | RD                            |                          |     |                               |  |  |

| REG_<br>MAGIC_NO       | 1     |                            |     |                                               | RD                            |                          |     |                               |  |  |

| REG_HW_<br>VER         | 2     |                            |     |                                               | RD                            |                          |     |                               |  |  |

| REG_SW_<br>VER         | 3     |                            |     |                                               | RD                            |                          |     |                               |  |  |

| REG_SF                 | 4     | WR                         |     | Non-<br>retentive                             | RD                            |                          |     |                               |  |  |

| REG                    | 5     |                            |     |                                               |                               |                          |     |                               |  |  |

|                        | ·     |                            |     |                                               |                               |                          |     |                               |  |  |

| REG                    | 13    |                            |     |                                               |                               |                          |     |                               |  |  |

| REG_WR_<br>ADR         | 14    |                            |     |                                               | RD                            |                          |     |                               |  |  |

| REG_RD_<br>ADR         | 15    |                            |     |                                               | RD                            |                          |     |                               |  |  |

| REG_DIAG1              | 16    |                            |     |                                               | RD                            |                          |     | RD                            |  |  |

| Designation             |    | Process<br>output<br>interface | Storage<br>in<br>module | Process<br>input<br>interface | Param-<br>eter<br>interface | Diagnos-<br>tics<br>interface |

|-------------------------|----|--------------------------------|-------------------------|-------------------------------|-----------------------------|-------------------------------|

| REG                     | 17 |                                |                         |                               |                             |                               |

|                         |    |                                |                         |                               |                             |                               |

| REG                     | 19 |                                |                         |                               |                             |                               |

| REG_PARA1               | 20 | WR                             | Reten-<br>tive          | RD                            | WR                          |                               |

| REG                     | 21 |                                |                         |                               |                             |                               |

|                         |    |                                |                         |                               |                             |                               |

| REG                     | 31 |                                |                         |                               |                             |                               |

| REG_GRAY_<br>POS        | 32 |                                |                         | RD                            |                             |                               |

| REG_SSI_<br>FRAME       | 33 |                                |                         | RD                            |                             |                               |

| REG_CMP1                | 34 | WR                             | Non-<br>retentive       | RD                            |                             |                               |

| REG_CMP2                | 35 | WR                             | Non-<br>retentive       | RD                            |                             |                               |

| REG                     | 36 |                                |                         |                               |                             |                               |

|                         |    |                                |                         |                               |                             |                               |

| REG                     | 47 |                                |                         |                               |                             |                               |

| REG_<br>LOWER_<br>LIMIT | 48 | WR                             | Reten-<br>tive          | RD                            |                             |                               |

| REG_<br>UPPER_<br>LIMIT | 49 | WR                             | Reten-<br>tive          | RD                            |                             |                               |

| REG_<br>OFFSET          | 50 | WR                             | Reten-<br>tive          | RD                            |                             |                               |

| REG_SSI_<br>MASK        | 51 | WR                             | Reten-<br>tive          | RD                            |                             |                               |

| REG                     | 52 |                                |                         |                               |                             |                               |

General product description

| Designation |    | Process<br>output<br>interface | Storage<br>in<br>module | Process<br>input<br>interface | Param-<br>eter<br>interface | Diagnos-<br>tics<br>interface |

|-------------|----|--------------------------------|-------------------------|-------------------------------|-----------------------------|-------------------------------|

| REG         | 63 |                                |                         |                               |                             |                               |

|             |    |                                | etentive regi<br>nes.   | sters can be                  | written up to               | 0 100,000                     |

# 1 Product Description General product description

#### Comparison value 1, Comparison value 2

The recorded encoder position can be compared with two loadable values. The character "x" below stands for "1" or "2". The register contents are loaded into the register REG CMPx using in a write operation. The comparison functions are activated by setting bit  $EN_CMPx = 1$  in the process output data. The results of the continuous comparison operations are displayed in the process input data via STS CMPx, REL CMPx and FLAG CMPx. Bit REL CMPx indicates as the actual status message the relation of the actual value (register content of REG SSI POS) to the comparison value (register content of REG CMPx). Bit STS CMPx is non-retentive and indicates whether the current actual value (REG SSI POS) and the comparison value (REG CMPx) match. FLAG CMPx is also used as a marker to indicate that the status (REG SSI POS = REG CMPx) is present or lost. This bit must be reset by the application via the process output data using CLR CMPx = 1. If the comparator is inactive (EN CMPx = 0), the signals from STS CMPx, REL CMPx and FLAG CMPx are always zero.

General product description

| Comparator<br>enable | Process input data                            |                                                              | Process output<br>data                                     |

|----------------------|-----------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------|

| EN_CMPx = 0          | REL_CMPx = 0<br>STS_CMPx = 0<br>FLAG_CMPx = 0 |                                                              |                                                            |

| EN_CMPx = 1          | (REG_SSI_POS) <<br>(REG_CMPx)                 | REL_CMPx = 0<br>STS_CMPx = 0<br>FLAG_CMPx = Z <sub>0</sub> * | Reset the<br>FLAG_CMPx flag<br>with<br>CLR_CMPx = 1        |

|                      | (REG_SSI_POS) ><br>(REG_CMPx)                 | REL_CMPx = 1<br>STS_CMPx = 0<br>FLAG_CMPx = Z <sub>0</sub> * | Reset the<br>FLAG_CMPx flag<br>with<br>CLR_CMPx = 1        |

|                      | (REG_SSI_POS) =<br>(REG_CMPx)                 | REL_CMPx = 1<br>STS_CMPx = 1<br>FLAG_CMPx = 1                | Reset of<br>FLAG_CMPx not<br>possible when<br>values match |

\*The value  $\rm Z_0$  of this flag is 1 as soon as the comparison values match. The value stays 1 until it is reset.

#### Lower limit, upper limit

The recorded encoder position can be compared with up to two loadable limit values. The upper limit value must be entered in the REG\_UPPER\_LIMIT register and the lower limit value in REG\_LOWER\_LIMIT. Writing these registers with values that are different to the default values will activate the monitoring of the limits, and bits STS\_OFLW and STS\_UFLW will be enabled in the process input data. The diagnostics function will indicate the presence of values above or below the default values.

"Encoder value overflow" and "Encoder value underflow" signals will also indicate this via the acyclic diagnostics interface.

The limit values are set by default to the maximum and minimum value.

General product description

| Register                                                           | Process input data                    |              | Diagnostics                                 |

|--------------------------------------------------------------------|---------------------------------------|--------------|---------------------------------------------|

| access                                                             |                                       | 0            |                                             |

| REG_UPPER_LI<br>MIT at default<br>value<br>FFFFFFFF <sub>hex</sub> | STS_OFLW = 0                          |              | Value: 0                                    |

| Register<br>content of                                             | (REG_SSI_POS) <=<br>(REG_UPPER_LIMIT) | STS_OFLW = 0 | Value: 0                                    |

| REG_UPPER_LI<br>MIT less than<br>FFFFFFFF <sub>hex</sub>           | (REG_SSI_POS) ><br>(REG_UPPER_LIMIT)  | STS_OFLW = 1 | Value: 1<br>Text: Encoder<br>value overflow |

Table 1: Overflow of the encoder values

Table 2: Underflow of the encoder values

| Register<br>access                                                  | Process input data                    |              | Diagnostics                                  |

|---------------------------------------------------------------------|---------------------------------------|--------------|----------------------------------------------|

| REG_LOWER_<br>LIMIT at default<br>value<br>000000000 <sub>hex</sub> | STS_UFLW = 0                          |              | Value: 0                                     |

| Register<br>content of                                              | (REG_SSI_POS) >=<br>(REG_LOWER_LIMIT) | STS_UFLW = 0 | Value: 0                                     |

| REG_LOWER_<br>LIMIT greater<br>than 0                               | (REG_SSI_POS) <<br>(REG_LOWER_LIMIT)  | STS_UFLW = 1 | Value: 1<br>Text: Encoder<br>value underflow |

#### Offset function / load value

This function is activated by writing the REG\_OFFSET register with a value <> 0. The content of the register is then subtracted from the SSI encoder value and stored in REG\_SSI\_POS. All limit values, such as lower limit, upper limit, comparison value 1, comparison value 2 then refer to the newly calculated value (REG\_SSI\_POS).

The calculation is thus:

(REG\_SSI\_POS) = SSI encoder - (REG\_OFFSET)

This function can be deactivated by writing the REG\_OFFSET with zero.

#### Status messages of the SSI encoder

Some SSI encoders not only transfer the position value in the data frame that they transfer to the module but also supply additional status messages. It is useful to include these status messages in the application in order to analyse the measured value.

Writing the REG\_SSI\_MASK register allows up to four individual bits to be taken from the data frame of the SSI encoder and transferred to the SSI\_STSx bits of the process input data. It is also possible to output the "SSI encoder group diagnostics message" with an acyclic diagnostics operation when a status message is initiated.

Process

General product description

REG\_SSI\_MASK

| input data                 |              |                |                                                                                    |    |      |                    |       |       |    |

|----------------------------|--------------|----------------|------------------------------------------------------------------------------------|----|------|--------------------|-------|-------|----|

|                            | Byte         | B7             | B6                                                                                 | B5 | B4   | B3                 | B2    | B1    | B0 |

| SSI_STS0                   | 0            | EN_D0_<br>RMS0 | EN_D0_<br>DS                                                                       | Х  | SSI_ | FRAM               | E_BIT | _SEL0 |    |

| SSI_STS1                   | 1            | EN_D1_<br>RMS1 | EN_D1_<br>DS                                                                       | Х  | SSI_ | SSI_FRAME_BIT_SEL1 |       |       |    |

| SSI_STS2                   | 2            | EN_D2_<br>RMS2 | EN_D2_<br>DS                                                                       | Х  | SSI_ | SSI_FRAME_BIT_SEL2 |       |       |    |

| SSI_STS3                   | 3            | EN_D3_<br>RMS3 | EN_D3_<br>DS                                                                       | Х  | SSI_ | FRAM               | E_BIT | _SEL3 |    |

| Designation                |              | Value          | Description                                                                        |    |      |                    |       |       |    |

|                            | <b>Fulue</b> |                |                                                                                    |    |      |                    |       |       |    |

| EN_Dx_RMSx 0 <sup>1)</sup> |              |                | The transfer of the SSI status messages to the process input data is not activated |    |      |                    |       |       |    |

1 The transfer of the SSI status messages to the process input data is activated The evaluation of the SSI status messages for bit EN\_ Dx\_DS  $0^{1)}$ 0 of the diagnostics is not activated 1 The evaluation of the SSI status messages for bit 0 of the diagnostics is activated. SSI\_FRAME\_BIT\_ Definition of the selected bits in the frame of the 0-31 SEL SSI encoder to be evaluated or copied. Default:0

1) Default

The following applies to bit 0 (SSI group diagnostics) of the diagnostics interface and SSI\_DIAG of the process input data:

(SSI\_STS0 & EN\_D0\_DS) || (SSI\_STS1 & EN\_D1\_DS) || (SSI\_STS2 & EN\_D2\_DS) || (SSI\_STS3 & EN\_D3\_DS)

# 1 Product Description General product description

#### Resetting the register bank

If register REG\_SF is written with the signature:

"LD20" = 6C643230<sub>hex</sub>,

all default values of the retentive registers (incl. parameter registers) are reset.

If register REG\_SF is written with the signature:

"LD48" = 6C643438<sub>hex</sub>

all default values of the retentive registers except the parameter registers are reset.

Overwritten values are lost.

# 1 Product Description Technical features

**Technical features**

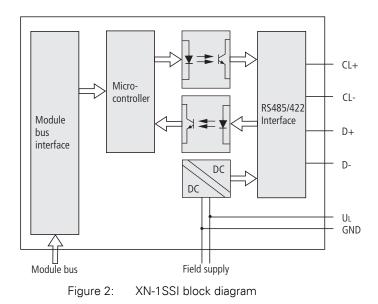

**Block diagram of the XN-1SSI**

Figure 1: XN-1SSI electronics module

#### **Technical data of the XN-1SSI**

The module is provided with two RS422 interfaces that form one SSI interface. One RS422 interface works as the clock generator for reading the data, which is then received on the other RS422 interface.

| Designation                                                        | XN-1SSI                                                 |

|--------------------------------------------------------------------|---------------------------------------------------------|

| Number of SSI interfaces                                           | 1                                                       |

| Transmission channels                                              | CL, D                                                   |

| Encoder voltage                                                    | 24 V DC (-15% / +20%)                                   |

| Encoder current                                                    | ≦ 500 mA                                                |

| Clock output type                                                  | RS422                                                   |

| Signal input type                                                  | RS422                                                   |

| RS422 connection type                                              | Four wire full-duplex<br>(clock output/signal input)    |

| Bit transmission rate                                              | ≦ 1 MHz (configurable),<br>default settings: 500 kBit/s |

| Cable impedance                                                    | 120 Ω                                                   |

| Bus terminating resistors                                          | internal                                                |

| RS422 cable length                                                 | ≦ 30 m                                                  |

| Nominal supply from supply terminal U <sub>L</sub> (range)         | 24 V DC (18 to 30 V DC)                                 |

| Nominal current consumption from supply terminal IL                | ≦ 25 mA (without encoder current)                       |

| Nominal current consumption from module bus I <sub>MB</sub>        | ≦ 50 mA                                                 |

| Power loss of the module                                           | normally 1 W                                            |

| Insulation voltage between interface and module bus/system voltage | 500 V <sub>rms</sub>                                    |

| Insulation voltage between interface and field voltage             | 500 V <sub>rms</sub>                                    |

Table 4: Technical data of the XN-1SSI

Technical features

| Designation                                                                       | XN-1SSI                          |

|-----------------------------------------------------------------------------------|----------------------------------|

| Electromagnetic compatibility (EMC)<br>according to IEC/EN 61000-6-2 (industrial) |                                  |

| ESD                                                                               | IEC/EN 61000-4-2                 |

| Electromagnetic fields                                                            | IEC/EN 61000-4-3                 |

| Burst                                                                             | IEC/EN 61000-4-4                 |

| Surge                                                                             | IEC/EN 61000-4-5                 |

| HF asymmetrical                                                                   | IEC/EN 61000-4-6                 |

| Damped oscillation                                                                | IEC/EN 61000-4-12                |

| Line-conducted emission/interference voltage                                      | IEC/EN 61000-6-4                 |

| Radiated high frequency emission                                                  | IEC/EN 61000-6-4:                |

|                                                                                   | IEC/CISPR 11 / EN 55011, Class A |

| Degree of protection                                                              | IP 20                            |

| Environment                                                                       |                                  |

| Operating temperature                                                             | 0 to +55 °C                      |

| Storage temperature                                                               | -25 to +85 °C                    |

| Relative humidity                                                                 | 15 to 95 % without condensation  |

# 1 Product Description Technical features

# Indication elements

| Table 5: Meaning o | t the | LEDs |

|--------------------|-------|------|

|--------------------|-------|------|

| 1SSI |     |       | Meaning                                 | Solution                                                                                                                                                                                                                                                                                                                                                                 |

|------|-----|-------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | DIA | Red   | Failure of module bus<br>communication  | Check whether more than<br>two adjacent electronics<br>modules have been pulled<br>out.<br>This applies to modules that<br>are located between the<br>gateway and this module.<br>Check the power supply of<br>the module bus.<br>Also check whether the SSI<br>encoder is fully functional<br>and the data cable check<br>has been supported in the<br>required manner. |

|      |     | OFF   | No error message or<br>diagnostics      | -                                                                                                                                                                                                                                                                                                                                                                        |

|      | UP  | Green | Direction of movement upwards           | _                                                                                                                                                                                                                                                                                                                                                                        |

|      | -   | OFF   | No upwards direction of movement        | _                                                                                                                                                                                                                                                                                                                                                                        |

|      | DN  | Green | Direction of movement downwards         | _                                                                                                                                                                                                                                                                                                                                                                        |

|      |     | OFF   | No downwards direc-<br>tion of movement | -                                                                                                                                                                                                                                                                                                                                                                        |

Base modules

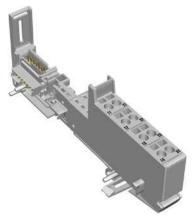

# **Base modules**

The following base modules can be used as terminals for connecting the XN-1SSI:

| Designation                   |             |

|-------------------------------|-------------|

| With tension clamp connectors | XN-S4T-SBBS |

| With screw terminal           | XN-S4S-SBBS |

# 1 Product Description Base modules

# Technical data of the base modules

| Table 6: | Technical data of the base modules |

|----------|------------------------------------|

|----------|------------------------------------|

| Designation                                                                | Value                                                                                    |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Measurement data                                                           | according to VDE 0611 Part 1/8.92 /<br>IEC/EN 60947-7-1                                  |

| Rated voltage                                                              | 250 V                                                                                    |

| Rated current                                                              | 17.5 A                                                                                   |

| Rated cross section                                                        | 1.5 mm <sup>2</sup>                                                                      |

| Rated surge voltage                                                        | 4 kV                                                                                     |

| Pollution degree                                                           | 2                                                                                        |

| TOP connection technology                                                  | Tension clamp or screw connection                                                        |

| Protection class                                                           | IP20                                                                                     |

| Insulation stripping length                                                | 8.0 to 9.0 mm / 0.32 to 0.36 inch                                                        |

| Max. wire range                                                            | 0.5 to 2.5 mm <sup>2</sup> /<br>0.0008 to 0.0039 inch <sup>2</sup> /<br>AWG 24 to AWG 14 |

| Crimpable wire                                                             |                                                                                          |

| "e" solid core H 07V-U                                                     | 0.5 to 2.5 mm <sup>2</sup> /<br>0.0008 to 0.0039 inch <sup>2</sup>                       |

| "f" flexible core H 07V-K                                                  | 0.5 to 1.5 mm <sup>2</sup> /<br>0.0008 to 0.0023 inch <sup>2</sup>                       |

| "f" with ferrules according to DIN 46228-1<br>(ferrules crimped gas-tight) | 0.5 to 1.5 mm <sup>2</sup> /<br>0.0008 to 0.0023 inch <sup>2</sup>                       |

| Test finger according to IEC/EN 60947-1                                    | A1                                                                                       |

# 1 Product Description Base modules

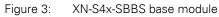

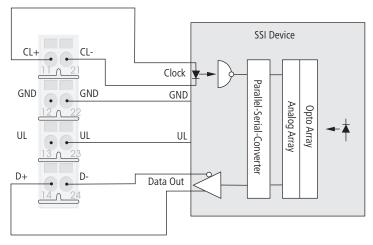

# Connection diagram for the SSI encoder

Figure 4: Connection diagram of XN-S4x-SBBS to an SSI encoder

| Signal designation |               |

|--------------------|---------------|

| CL                 | Clock         |

| D                  | Data          |

| GND                | Signal ground |

| UL                 | Voltage       |

# 2 Integrating the Module in PROFIBUS-DP

#### **PROFIBUS-DP** data image

#### Process input

The field input data is transferred from the connected field device to the XN-1SSI module.

The process input data is the data that is transferred to the PLC from the XN-1SS1 via a gateway.

This is transferred in an 8 byte format as follows:

- 4 bytes are used for representing the data that was read from the register with the address stated at REG\_RD\_ADR.

- When necessary, 1 byte represents the register address of the read data and an acknowledgement that the read operation was successful.

- 1 byte can be used to transfer status messages of the SSI encoder. This byte also contains an acknowledgement that the write operation to the register was successful and indication of an active write operation.

- 1 byte contains the results of comparison operations with the SSI encoder value.

- 1 byte contains messages concerning the communication status between the XN-1SSI module and the SSI encoder, as well as other results of comparison operations.

# 2 Integrating the Module in PROFIBUS-DP PROFIBUS-DP data image

The following table describes the structure of the  $8 \times 8$  bits of the process input data.

STS (or ERR) contains non-retentive status information, i.e. the bit concerned indicates the actual status.

FLAG describes a retentive flag that is set in the event of a particular event. The bit concerned retains the value until it is reset.

#### Structure of the data bytes in the PROFIBUS-DP fieldbus:

|        | Bit 7                | Bit 6              | Bit 5        | Bit 4         | Bit 3        | Bit 2        | Bit 1         | Bit 0        |

|--------|----------------------|--------------------|--------------|---------------|--------------|--------------|---------------|--------------|

| Byte 0 | REG_RD_              | _DATA, B           | yte 3        |               |              |              |               |              |

|        |                      |                    |              |               |              |              |               |              |

| Byte 3 | REG_RD_DATA, Byte 0  |                    |              |               |              |              |               |              |

| Byte 4 | REG_<br>RD_<br>ABORT | Х                  | REG_RI       | D_ADR (N      | ISB to LS    | B)           |               |              |

| Byte 5 | REG_<br>WR_<br>ACEPT | REG_<br>WR_<br>AKN | Х            | X             | SSI_<br>STS3 | SSI_<br>STS2 | SSI_<br>STS1  | SSI_<br>STS0 |

| Byte 6 | STS_<br>UP           | STS_<br>DN         | REL_<br>CMP2 | FLAG_<br>CMP2 | STS_<br>CMP2 | REL_<br>CMP1 | FLAG_<br>CMP1 | STS_<br>CMP1 |

| Byte 7 | STS_<br>STOP         | Х                  | Х            | ERR_<br>PARA  | STS_<br>UFLW | STS_<br>OFLW | ERR_<br>SSI   | SSI_<br>DIAG |

X = reserved

| Designation  | Value                   | Description                                                                                                                                                                                                                                                            |

|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REG_RD_DATA  | 0<br>2 <sup>32</sup> -1 | Content of the register to be read if<br>REG_RD_ABORT = 0. If REG_RD_ABORT = 1,<br>REG_RD_DATA = 0.                                                                                                                                                                    |

| REG_RD_ABORT | 0                       | The reading of the register stated at REG_RD_ADR was accepted and executed. The content of the register is located in the user data range (REG_RD_DATA Bytes 0-3).                                                                                                     |

|              | 1                       | The reading of the register stated at REG_RD_ADR was not accepted. The user data range (REG_RD_DATA Bytes 0-3) is zero.                                                                                                                                                |

| REG_RD_ADR   | 063                     | Address of the register containing the data shown<br>in the user data range (REG_RD_DATA Bytes 0-3)<br>of the process input data when REG_RD_ABORT =<br>0.                                                                                                             |

| REG_WR_ACEPT | 0                       | The writing of user data for process output to the register with the address stated at REG_WR_ADR in the process output data could not be executed.                                                                                                                    |

|              | 1                       | The writing of user process output data to the register with the address stated at REG_WR_ADR in the process output data was successfully completed.                                                                                                                   |

| REG_WR_AKN   | 0                       | No modification of the data in the register bank by process output, i.e. $REG_WR = 0 \rightarrow Chapter$ "Process output".<br>A write job would be accepted with the next tele-<br>gram of process output data.<br>(handshake for data transmission to the register.) |

|              | 1                       | A modification of the register contents by a<br>process output was initiated, i.e. REG_WR = 1<br>$\rightarrow$ Chapter "Process output".<br>A write job would not be accepted with the next<br>telegram of process output data.                                        |

## Meaning of the data bits (process input data):

# 2 Integrating the Module in PROFIBUS-DP PROFIBUS-DP data image

| Designation        | Value | Description                                                                                                                                      |  |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SSI_STS3           | 0     | These four bits transfer the status bits of the SS                                                                                               |  |

|                    | 1     | encoder with the status messages of the SSI module. With some SSI encoders, the status bits                                                      |  |

| SSI_STS2           | 0     | are transferred together with the position value.                                                                                                |  |

|                    | 1     |                                                                                                                                                  |  |

| SSI_STS1           | 0     |                                                                                                                                                  |  |

|                    | 1     |                                                                                                                                                  |  |

| SSI_STS0           | 0     |                                                                                                                                                  |  |

|                    | 1     |                                                                                                                                                  |  |

| STS_UP<br>(LED UP) | 0     | The SSI encoder values are decremented or the values are constant.                                                                               |  |

|                    | 1     | The SSI encoder values are incremented.                                                                                                          |  |

| STS_DN<br>(LED DN) | 0     | The SSI encoder values are incremented or the values are constant.                                                                               |  |

|                    | 1     | The SSI encoder values are decremented.                                                                                                          |  |

| REL_CMP2           | 0     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) < (REG_CMP2)                                        |  |

|                    | 1     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) ≧ (REG_CMP2)                                        |  |

| FLAG_CMP2          | 0     | Default status, i.e. the register contents have not yet matched (REG_SSI_POS) = (REG_CMP2) since the last reset.                                 |  |

|                    | 1     | The contents of the registers match<br>(REG_SSI_POS) = (REG_CMP2).<br>This marker must be reset with CLR_CMP2 = 1 in<br>the process output data. |  |

| STS_CMP2           | 0     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) k (REG_CMP2)                                        |  |

|                    | 1     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) = (REG_CMP2)                                        |  |

### 2 Integrating the Module in PROFIBUS-DP PROFIBUS-DP data image

| Designation | Value | Description                                                                                                                                       |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| REL_CMP1    | 0     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) < (REG_CMP1)                                         |

|             | 1     | A comparison of the register contents has<br>produced the following result:<br>(REG_ SSI_POS) ≧ (REG_CMP1)                                        |

| FLAG_CMP1   | 0     | Default status, i.e. the register contents have not yet matched (REG_SSI_POS) = (REG_CMP1) since the last reset.                                  |

|             | 1     | The contents of the registers match:<br>(REG_SSI_POS) = (REG_CMP1). This marker must<br>be reset when CLR_CMP1 = 1 in the process<br>output data. |

| STS_CMP1    | 0     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) k (REG_CMP1)                                         |

|             | 1     | A comparison of the register contents has<br>produced the following result:<br>(REG_ SSI_POS) = (REG_CMP1)                                        |

| STS_STOP    | 0     | The SSI encoder is read cyclically.                                                                                                               |

|             | 1     | Communication with the SSI encoder is stopped as STOP = 1 (process output) or ERR_PARA = 1.                                                       |

| ERR_PARA    | 0     | The parameter set of the module has been accepted.                                                                                                |

|             | 1     | Operation of the module is not possible with the present parameter set.                                                                           |

| STS_UFLW    | 0     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) ≧ (REG_LOWER_LIMIT)                                  |

|             | 1     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) < (REG_LOWER_LIMIT)                                  |

## 2 Integrating the Module in PROFIBUS-DP

PROFIBUS-DP data image

| Designation | Value | Description                                                                                                      |

|-------------|-------|------------------------------------------------------------------------------------------------------------------|

| STS_OFLW    | 0     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) ≦ (REG_UPPER_LIMIT) |

|             | 1     | A comparison of the register contents has<br>produced the following result:<br>(REG_SSI_POS) > (REG_UPPER_LIMIT) |

| ERR_SSI     | 0     | SSI encoder signal present.                                                                                      |

|             | 1     | SSI encoder signal faulty. (e.g. due to a cable break).                                                          |

| SSI_DIAG    | 0     | No enabled status signal is active (SSI_STSx = 0).                                                               |

|             | 1     | At least one enabled status signal is active $(SSI\_STSx = 1)$ .                                                 |

#### **Process output**

The field output data is transferred from the XN-1SSI module to the connected field device.

The process output data is the data that is output from the PLC to the XN-1SSI module via a gateway.

This is transferred in an 8 byte format as follows:

- 4 bytes are used for representing the data that is to be written to the register with the address specified at REG\_WR\_DATA.

- 1 byte contains the register address for the data that is to be read with the next response tele-gram.

- 1 byte contains the register address of the data to be written to bytes 0 to 3 of this telegram and a write request.

- 1 byte is used for controlling the comparison operations.

- 1 byte contains a Stop bit for interrupting communication with the encoder.

# 2 Integrating the Module in PROFIBUS-DP PROFIBUS-DP data image

|        |            |                     | data):       |              |             |       |              |             |

|--------|------------|---------------------|--------------|--------------|-------------|-------|--------------|-------------|

|        | Bit 7      | Bit 6               | Bit 5        | Bit 4        | Bit 3       | Bit 2 | Bit 1        | Bit 0       |

| Byte 0 | REG_WR_    | _DATA, E            | Syte 3       |              |             |       |              |             |

|        |            |                     |              |              |             |       |              |             |

| Byte 3 | REG_WR_    | REG_WR_DATA, Byte 0 |              |              |             |       |              |             |

| Byte 4 | Х          | Х                   | X REG_RD_ADR |              |             |       |              |             |

| Byte 5 | REG_<br>WR | Х                   | REG_W        | /R_ADR       |             |       |              |             |

| Byte 6 | Х          | Х                   | Х            | CLR_<br>CMP2 | EN_<br>CMP2 | Х     | CLR_<br>CMP1 | EN_<br>CMP1 |

| Byte 7 | STOP       | Х                   | Х            | Х            | Х           | Х     | Х            | Х           |

# Structure of the data bytes (process output data):

X = reserved

#### Meaning of the data bits (process output data):

| Designation | Value                | Description                                                                                                                                                                                                                                |

|-------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REG_WR_DATA | 0 2 <sup>32</sup> -1 | Value to be written to the register with the address stated at REG_WR_ADR.                                                                                                                                                                 |

| REG_RD_ADR  | 063                  | Address of the register to be read. If the read operation is successful (REG_RD_ABORT = 0), the user data is located in REG_RD_DATA of the process input data (bytes $4 - 7$ ).                                                            |

| REG_WR      | 0                    | Default status, i.e. there is no request to over-<br>write the content of the register with the address<br>stated at REG_WR_ADR with REG_WR_DATA.<br>Bit REG_WR_AKN ( $\rightarrow$ Chapter "Process input")<br>is reset (0) if necessary. |

|             | 1                    | Request to overwrite the content of the register with the address stated at REG_WR_ADR with REG_WR_DATA.                                                                                                                                   |

| REG_WR_ADR  | 063                  | Address of the register to be written with REG_WR_DATA.                                                                                                                                                                                    |

| CLR_CMP2    | 0                    | Default status, i.e. no reset of FLAG_CMP2 active.                                                                                                                                                                                         |

|             | 1                    | Reset of FLAG_CMP2 active                                                                                                                                                                                                                  |

### 2 Integrating the Module in PROFIBUS-DP PROFIBUS-DP data image

| Designation | Value | Description                                                                                                                                           |

|-------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN_CMP2     | 0     | Default status, i.e. the data bits REL_CMP2, STS_CMP2 and FLAG_CMP2 always have the value 0, irrespective of the actual SSI encoder value.            |

|             | 1     | Comparison active, i.e. the data bits REL_CMP2, STS_CMP2 and FLAG_CMP2 have a value based on the result of the comparison with the SSI encoder value. |

| CLR_CMP1    | 0     | Default status, i.e. reset of FLAG_CMP1 not active.                                                                                                   |

|             | 1     | Reset of FLAG_CMP1 active                                                                                                                             |

| EN_CMP1     | 0     | Default status, i.e. the data bits REL_CMP1,<br>STS_CMP1 and FLAG_CMP1 always have the<br>value 0, irrespective of the actual SSI encoder<br>value.   |

|             | 1     | Comparison active, i.e. the data bits REL_CMP1, STS_CMP1 and FLAG_CMP1 have a value based on the result of the comparison with the SSI encoder value. |

| STOP        | 0     | Request to read the SSI encoder cyclically                                                                                                            |

|             | 1     | Request to interrupt communication with the encoder                                                                                                   |

#### 2 Integrating the Module in PROFIBUS-DP PROFIBUS-DP data image

#### Diagnostics

The parameter setting for the PROFIBUS-DP gateway provides the Gateway Diagnostics parameter for selecting between two different diagnostics displays. Choose "Devices, ID, Channel Diagnostics" to select more detailed diagnostics indication. The diagnostics message will then consist of the following elements:

- 2 bytes of gateway diagnostics (device-related diagnostics)

- 64 bits of ID-specific diagnostics

- n x 3 bytes of channel-specific diagnostics (n: number of channels with active diagnostics)

With channel-specific diagnostics the use of an error number enables the type of error to be indicated as text (e.g. Parameter error).

When "Device-related Diagnostics" is selected, an abbreviated diagnostics message is generated that simply shows the gateway diagnostics (device-related diagnostics). The diagnostics bytes of all station modules are attached that support diagnostics.

| Name of error type           | Position<br>(Type 2) | Value | Description                                                                                              |

|------------------------------|----------------------|-------|----------------------------------------------------------------------------------------------------------|

| SSI group diagnos-<br>tics   | Bit 0                | 0     | No enabled status signal active:<br>SSI_STSx = 0 or no status<br>messages of the SSI encoder<br>present. |

|                              |                      | 1     | At least one enabled status signal is active: SSI_STSx = 1.                                              |

| Wire-break                   | Bit 1                | 0     | SSI encoder signal present.                                                                              |

|                              |                      | 1     | SSI encoder signal faulty (e.g. due to a cable break).                                                   |

| Encoder values over-<br>flow | Bit 2                | 0     | SSI encoder value below / equal to upper limit.                                                          |

|                              |                      | 1     | SSI encoder value above upper limit. Overflow occurred.                                                  |

| Encoder values<br>underflow  | Bit 3                | 0     | SSI encoder value above / equal to lower limit.                                                          |

|                              |                      | 1     | SSI encoder value below lower limit. Underflow occurred.                                                 |

| Parameter error              | Bit 4                | 0     | The parameter set of the module has been accepted.                                                       |

|                              |                      | 1     | Operation of the module is not possible with the present parameter set.                                  |